You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

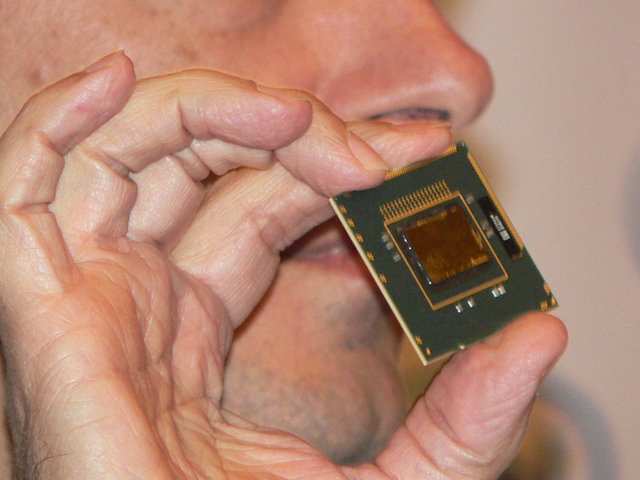

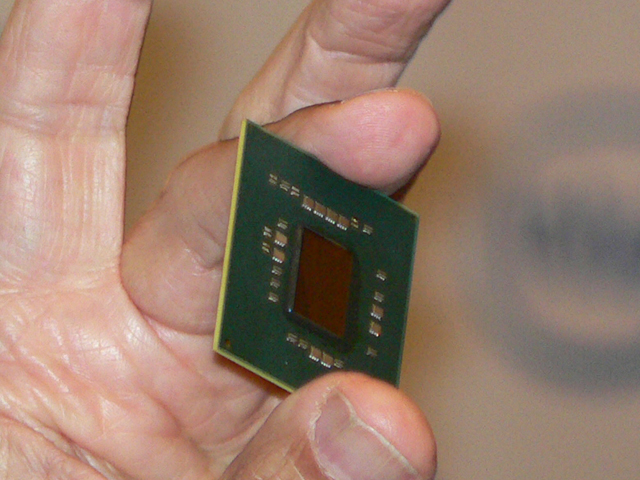

Nehalem CPU Die Show

- Autor do tópico Zarolho

- Data Início

Koncaman

Utilizador Saloio

Não percebi uma coisa: na imagem onde aparece o gestor de tarefas são 8 ou 16 cores?

É que se são 8 cores significa que vamos ter duas threads por core tal como o hyper-threading?

2 unidades de processamento logico por core:

mas isto ja não é novidade em processadores multi-core.

Esta arquitectura vem com uma serie de inovações inteligentes

Intel QuickPath (a.ka. CSI),

controlador DDR3 integrado,

até 4 canais de memoria,

processo de fabrico de 45nm

Novos sets de instruções

e parece que ha intenção de fazer uma coisa tipo fusion: integrar um GPU na mesma package do CPU (excepto nos modelos de 8 cores, provavelmente por questões de espaço no package)

... resta saber se a implementação será a melhor, e se a estabilidade se aguentará com tanta inovação.

Última edição:

WindWalker

Power Member

Portanto, o HT não morreu...passa a existir em 8 cores.

Um monstro. Este promete!

Só não percebi porque o chipset não vai passar a ser single chip, ainda vejo o ICH + I/O hub aka northbridge.

O quickpath vai funcionar tal e qual o HT, com até 3 lanes entre os cpus. powaa!

E o "core" é enorme até, não sei como vão meter 8 cores single package!

Só não percebi porque o chipset não vai passar a ser single chip, ainda vejo o ICH + I/O hub aka northbridge.

O quickpath vai funcionar tal e qual o HT, com até 3 lanes entre os cpus. powaa!

E o "core" é enorme até, não sei como vão meter 8 cores single package!

Koncaman

Utilizador Saloio

Memo para AMD ja se voltou a usar north e south bridge, quase a partir do momento em que chegou o PCI-express.

é uma opção mais modular, no northbridge ligas os componentes essenciais, incluindo o south bridge, e comunicas com o CPU, defines a performance do nucleo duro do sistema.

no south bridge defines os "extras".

Os fabricantes de motherboards ficam com muitas mais combinações de chips à disposição (dado que normalmente com um northbridge pode-se montar qualquer southbridge da mesma linha), e o consumidor agradece.

a ideia do quickpath é precisamente concorrer com o HyperTransport... no entanto, alguma coisa tem que ser diferente, por causa das patentes.

o tamanho do core é essencialmente culpa da cache, no entanto, o processo de 45nm, ha de o tornar suficientemente pequeno, a ponto de ser possivel incluir tudo no mesmo package.

é uma opção mais modular, no northbridge ligas os componentes essenciais, incluindo o south bridge, e comunicas com o CPU, defines a performance do nucleo duro do sistema.

no south bridge defines os "extras".

Os fabricantes de motherboards ficam com muitas mais combinações de chips à disposição (dado que normalmente com um northbridge pode-se montar qualquer southbridge da mesma linha), e o consumidor agradece.

a ideia do quickpath é precisamente concorrer com o HyperTransport... no entanto, alguma coisa tem que ser diferente, por causa das patentes.

o tamanho do core é essencialmente culpa da cache, no entanto, o processo de 45nm, ha de o tornar suficientemente pequeno, a ponto de ser possivel incluir tudo no mesmo package.

Apenas a ATI E VIA usa este esquema

A nvidia foi sempre single chip, tirando os chipsets 16x-16x que eram dual chip.

embora 2 chips permite modularidade, acaba por ter maior consumo electrico e espaço ocupado na board

As DFI NF4 tinham um layout perfeito com muito espaço, graças a isso

A nvidia foi sempre single chip, tirando os chipsets 16x-16x que eram dual chip.

embora 2 chips permite modularidade, acaba por ter maior consumo electrico e espaço ocupado na board

As DFI NF4 tinham um layout perfeito com muito espaço, graças a isso

Koncaman

Utilizador Saloio

Apenas a ATI E VIA usa este esquema

A nvidia foi sempre single chip, tirando os chipsets 16x-16x que eram dual chip.

embora 2 chips permite modularidade, acaba por ter maior consumo electrico e espaço ocupado na board

As DFI NF4 tinham um layout perfeito com muito espaço, graças a isso

também tinham um layout "perfeito" graças a um chipset cooler de baixo perfil...

Agora com a moda dos heat pipes, quase qualquer board pode ter 2 chips, sem estorvar os restantes componentes. quanto ao consumo electrico... não creio que seja dos componnetes cujo o consumo seja mais significante.

também acredito que com a passagem do controlador de memoria do north bridge para o CPU se poupe algum consumo no balanço final (assumindo que o processo de 45nm, é mais eficiente energeticamente, que o processo usado nos chipsets).

o Nehalem tem um desenho modular, vai ser mais facil meter e tirar cores e basta n aumentar a cache q já cabem 8 cores.E o "core" é enorme até, não sei como vão meter 8 cores single package!

blastarr

Power Member

Apenas a ATI E VIA usa este esquema

A nvidia foi sempre single chip, tirando os chipsets 16x-16x que eram dual chip.

embora 2 chips permite modularidade, acaba por ter maior consumo electrico e espaço ocupado na board

As DFI NF4 tinham um layout perfeito com muito espaço, graças a isso

Isso é consequência do facto de as northbridges da Nvidia poderem funcionar como southbridges, ou mesmo de ser possível emparelhar duas northbridges iguais (veja-se o caso da nForce "680a", que consiste em duas northbridges nForce 570 SLI ligadas por Hypertransport -um protocolo que a Nvidia reutiliza com frequência, desde o nForce original para Athlon até ao nForce 680i SLI para Intel-).

Ou até pode dar-se o caso de combinar de forma não-oficial uma northbridge para Intel com uma Northbridge/Southbridge para AMD, como a Gigabyte fez ao usar o NF4 SLI como southbridge nesta mobo para Intel há uns anos...

O facto de a Intel também passar a ter controlador de memória integrado poderia indicar que só agora seria possível realizar essa possibilidade de chipsets single-chip nessa plataforma, mas a verdade é que o próximo IGP da Nvidia para Intel vai ser single-chip, e chegará aínda antes do "Nehalem".

Até pode ser semelhante ao IGP que eles vão lançar em breve para AMD, a juntar aos nForce 780a/750a de topo.

Última edição:

É pena com esta modularidade nunca ter aparecido uma combinação northbridge com IGP poderoso + southbridge "poderoso", suportando x16/x16 e ainda video onboard para backup

Mas penso que isto virá a tona com o hybrid SLI.

Sobre o Nehalem, o octo core será nativo ou 2 dies separadas?

Mas penso que isto virá a tona com o hybrid SLI.

Sobre o Nehalem, o octo core será nativo ou 2 dies separadas?

Kursk_crash

Banido

Eis o 1º CPU Intel com controlador de memória integrado... Mais uma "bandeira" exclusiva da AMD que cai....

Pelo contrário. É o reconhecer por parte da Intel que o Controlador integrado pode trazer benefícios.. algo que a Intel sempre ridicularizou e sempre anunciou como inútil e como pormenor sem impotância, estará brevemente em toda a linha de cpu's intel !!

Uma aposta ganha da AMD

Zarolho

Power Member

Pelo contrário. É o reconhecer por parte da Intel que o Controlador integrado pode trazer benefícios.. algo que a Intel sempre ridicularizou e sempre anunciou como inútil e como pormenor sem impotância, estará brevemente em toda a linha de cpu's intel !!

Uma aposta ganha da AMD

Não interpretaste bem o meu comentário... É uma "bandeira", porque se fizermos uma leitura em que acreditamos que um controlador de memória integrado é uma mais valia face á ausência dele, então deixou de ser uma vantagem (bandeira) dado que ambos fabricantes irão estar a operar em circunstancia muito idênticas, possibilitando assim uma analise mais facil sobre a performance entre plataformas diferentes.

Sobre os benefícios de um controlador integrado, certamente que tem as suas vantagens, mas só quando perante determinadas circunstancias técnicas, prova disso são os actuais C2D e C2Q que lideram o mercado sem controlador integrado e é muito provável que continuaram a ser muito competitivos com os novos Qcore nativos da AMD K10 com controlador integrado.

A ver vamos... Em breve.

blastarr

Power Member

Muitos MB de cache L3 e poucos de L2,it seems like Barcelona

Há uma diferença crucial.

No "Barcelona" tens 2MB de L3 partilhados pelos 4 cores, para além dos 512KB de L2 por core).

Aqui tens 2MB de L3 por core, dedicados (total de 8MB) e os mesmos 512KB de L2 por core.

Outra diferença relevante é a confirmação do que eu já tinha escrito neste fórum, o controlador de memória DDR3 "Triple Channel" -192 bit- (no "Barcelona" é dual-channel de 128bit).

Contudo, seria interessante saber qual o tamanho das caches L1.

Última edição:

Zar0n

Power Member

Há uma diferença crucial.

No "Barcelona" tens 2MB de L3 partilhados pelos 4 cores, para além dos 512KB de L2 por core).

Aqui tens 2MB de L3 por core, dedicados (total de 8MB) e os mesmos 512KB de L2 por core.

A L3 cache partilhada é superior principalmente em aplicações multicore e por altura que este CPU sair já n devem ser só 2MB no cpu da AMD.

Se é para ser dedicada tanta L3 vs L2 deve ter haver com yields e consumo do CPU, vamos ver se conseguem continuar a aumentar os MHz agr k é quadcore nativo.

Mas sem duvida que este retira mt's das vantagem da arquitectura da AMD.

Axo k esta tem k se livrar do SOI e mudar para algo como DOI pk se n sobe os MHz n vai conseguir ser competitiva contra uma arquitectura "equivalente".

Última edição:

blastarr

Power Member

A L3 cache partilhada é superior principalmente em aplicações multicore e por altura que este CPU sair já n devem ser só 2MB no cpu da AMD.

Se é para ser dedicada tanta L3 vs L2 deve ter haver com yields e consumo do CPU, vamos ver se conseguem continuar a aumentar os MHz agr k é quadcore nativo.

Mas sem duvida que este retira mt's das vantagem da arquitectura da AMD.

Axo k esta tem k se livrar do SOI ou mudar para algo como DOI pk se n sobe os MHz n vai conseguir ser competitiva contra uma arquitectura "equivalente".

A L3 partilhada pelos cores é provavelmente a razão dos terríveis níveis de latência que o Barcelona revela nesse aspecto.

Se aínda fosse L2, o efeito era minorado, mas assim...

http://techreport.com/articles.x/13176/3

Zar0n

Power Member

A L3 partilhada pelos cores é provavelmente a razão dos terríveis níveis de latência que o Barcelona revela nesse aspecto.

Se aínda fosse L2, o efeito era minorado, mas assim...

http://techreport.com/articles.x/13176/3

Esse teste n é equivalente aos que vais encontrar em AM2+, tanto pelos Mhz dos CPU como pela velocidade da NB.

Quanto à L2 partilhada torna-se mt mais complicado com o aumento do nº de cores, aliás basta ver o caminho que o Nehalem segue.

Claro k a Intel (como sempre) pode-se dar ao luxo de colocar tanta L3 dedicada, mas nos CPU's futuros certamente vamos ver algum tipo de memoria (pode n ser cache) partilhada por tds os cores.

blastarr

Power Member

Esse teste n é equivalente aos que vais encontrar em AM2+, tanto pelos Mhz dos CPU como pela velocidade da NB.

Quanto à L2 partilhada torna-se mt mais complicado com o aumento do nº de cores, aliás basta ver o caminho que o Nehalem segue.

Claro k a Intel (como sempre) pode-se dar ao luxo de colocar tanta L3 dedicada, mas nos CPU's futuros certamente vamos ver algum tipo de memoria (pode n ser cache) partilhada por tds os cores.

Isso não é novidade, a Intel já anunciou há algum tempo a "stacked memory".

To solve the problem on the new chip, they used a hardware-based thread scheduler and faster on-chip memory caches, optimizing the way data flows from memory into each core. To improve the design, Intel researchers plan to add a layer of "3D stacked memory" under the chip to minimize the time and power required to feed the cores with data. Next, they will create a mega-chip that uses general purpose cores instead of the floating-point units used in the current design.

O próximo passo nesta "mesh 3D" será trocar as ligações de cobre por ligações ópticas, com recurso a lasers de silício que a Intel também já anunciou.