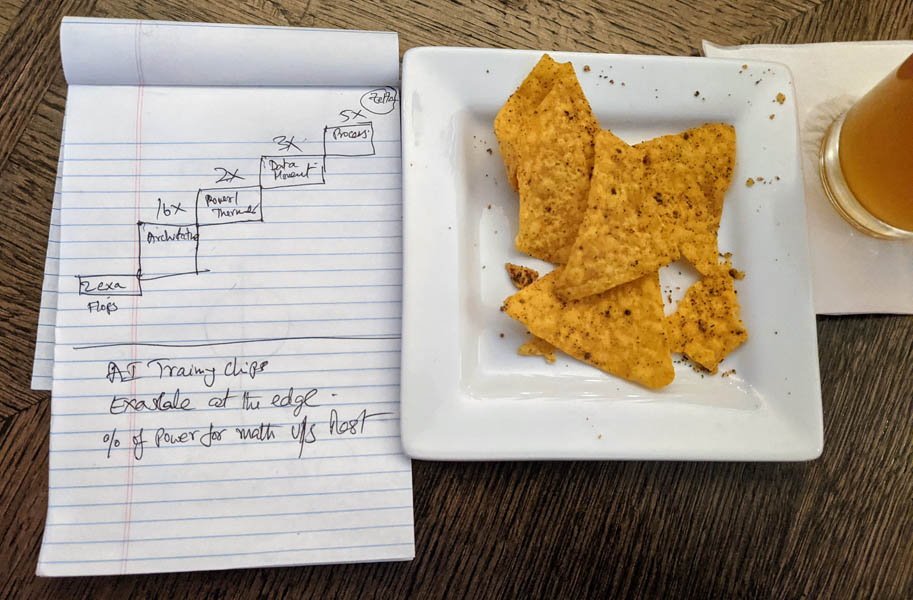

RK: Some of them have opportunities beyond those numbers. For example, when we say ‘power and thermals’, it's also power delivery - if you just look at the way we build computers today, just the regulated losses that you have on how we deliver current to the chip. With integration at a system scale, there are opportunities - not just Intel identified opportunities, but many folks outside Intel have called things out, such as driving higher voltages [in the backplane] to drive lower current in. So there are opportunities there. The data center folks have been taking advantage of some of this stuff already, as well as the big hyperscalers - but there is more available with integration.

But you said something very interesting - if we viewed Zettascale as a collection of components, such as GPUs, CPUs, and memories and all - each of them are fed separate power. You could have a 300 watt GPU and a 250 watt CPU. That's one way of doing the math. But if I have X amount of compute, what amount of current is needed to deliver to that compute - there are large power losses today because each component has its own separate power delivery mechanisms, so we waste a lot of energy.

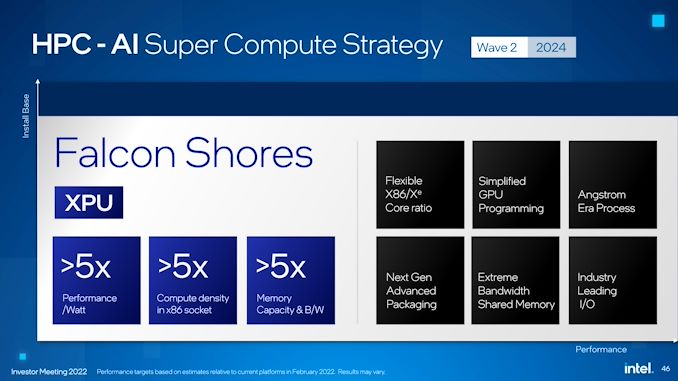

The key idea behind all of this stuff is the ‘unit of compute’. Today, when I say ‘unit of compute’, we mean that a CPU is a unit of compute, or a single GPU is a unit of compute. There is no reason why they have to be that way. That's what we define today for market reasons, for product reasons and all that stuff, but what if your new ‘unit of compute’ is something different? Each unit of compute has a particular overhead - beyond the core compute, it’s about delivering power to a thermal solution. There’s cost too, right? There bunch of materials on the board and all the repetitive components could potentially be combined for lower overall losses.

Historically, this is one of the foundations of Moore's Law. Integration with Integration. We drove this extraordinary foundation, and now we have a supercomputer in your pocket in a phone. No reason that aspect of Moore's law needs to stop, because there's still an opportunity just even beyond transistors. Just the integration - integration can drive some order of magnitude efficiencies.