Terminologia AMD GPU "um core" é "um "Stream Processor", não há Shader Units

A resposta simples à tua pergunta é: não sei!

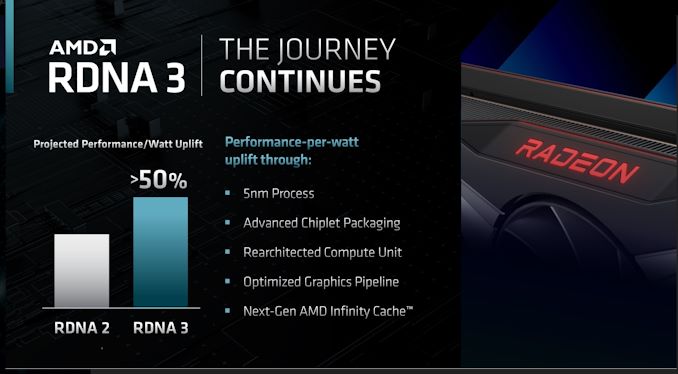

Problema: a forma como a AMD agrupa os ditos mudou das GCN para as RDNA1/2 e vai mudar para as RDNA3

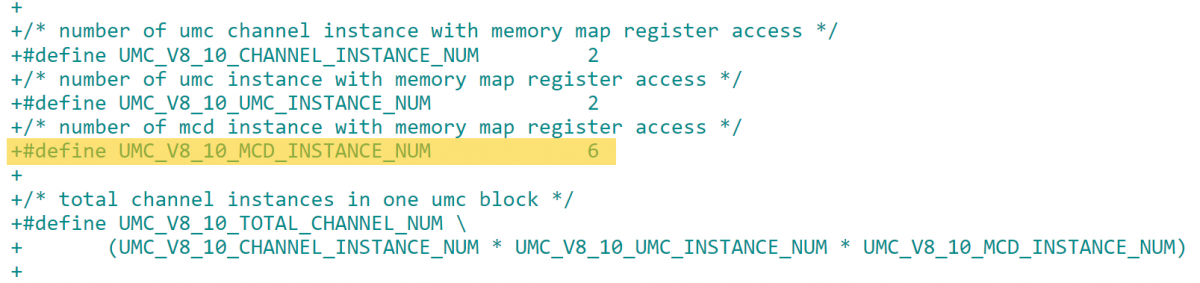

De 1CU=64SP passou-se para 1WGP=2CU=128SP (1CU=64SP), o "rácio" manteve-se mas agrupados de forma diferente, e agora vamos passar para 1WGP=2CU=256SP (1CU=128SP) ou seja duplicou.

O que explica como a 6900 XT com 80CU (ou

Compute

Units) tenha 5120SP (

Stream

Processors) ou seja (5120/80=64) mas a 7900XT com apenas 96CU tenha os tais 12288SP (12288/96=128).

O que significa na prática?

Sem saber o que mudou no resto do Front End ou do Back End é difícil saber, pois tudo indicaria que poderia haver um bottleneck, uma vez que apenas as "unidades de execução" duplicaram.

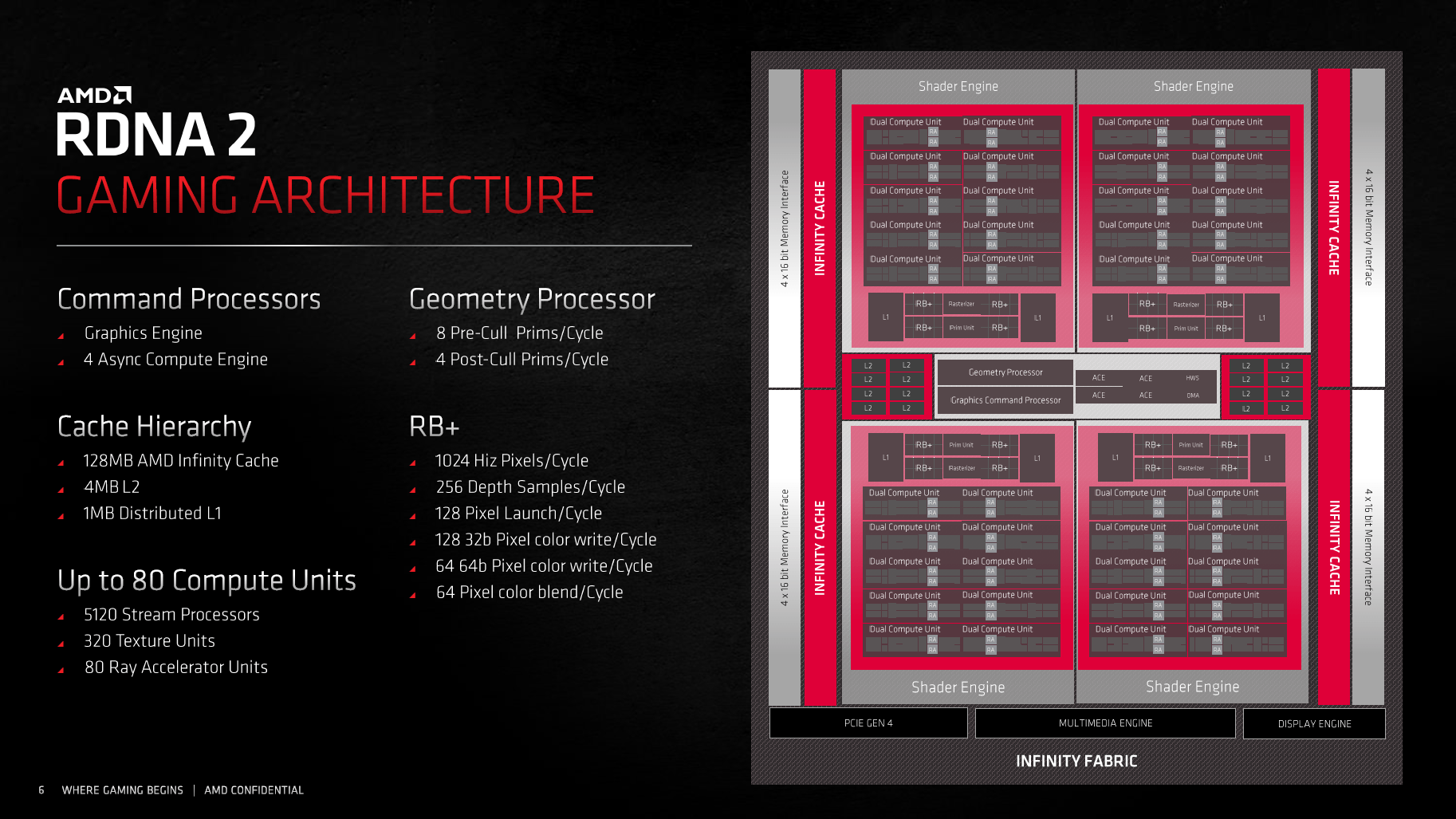

Este é o diagrama da 6900XT

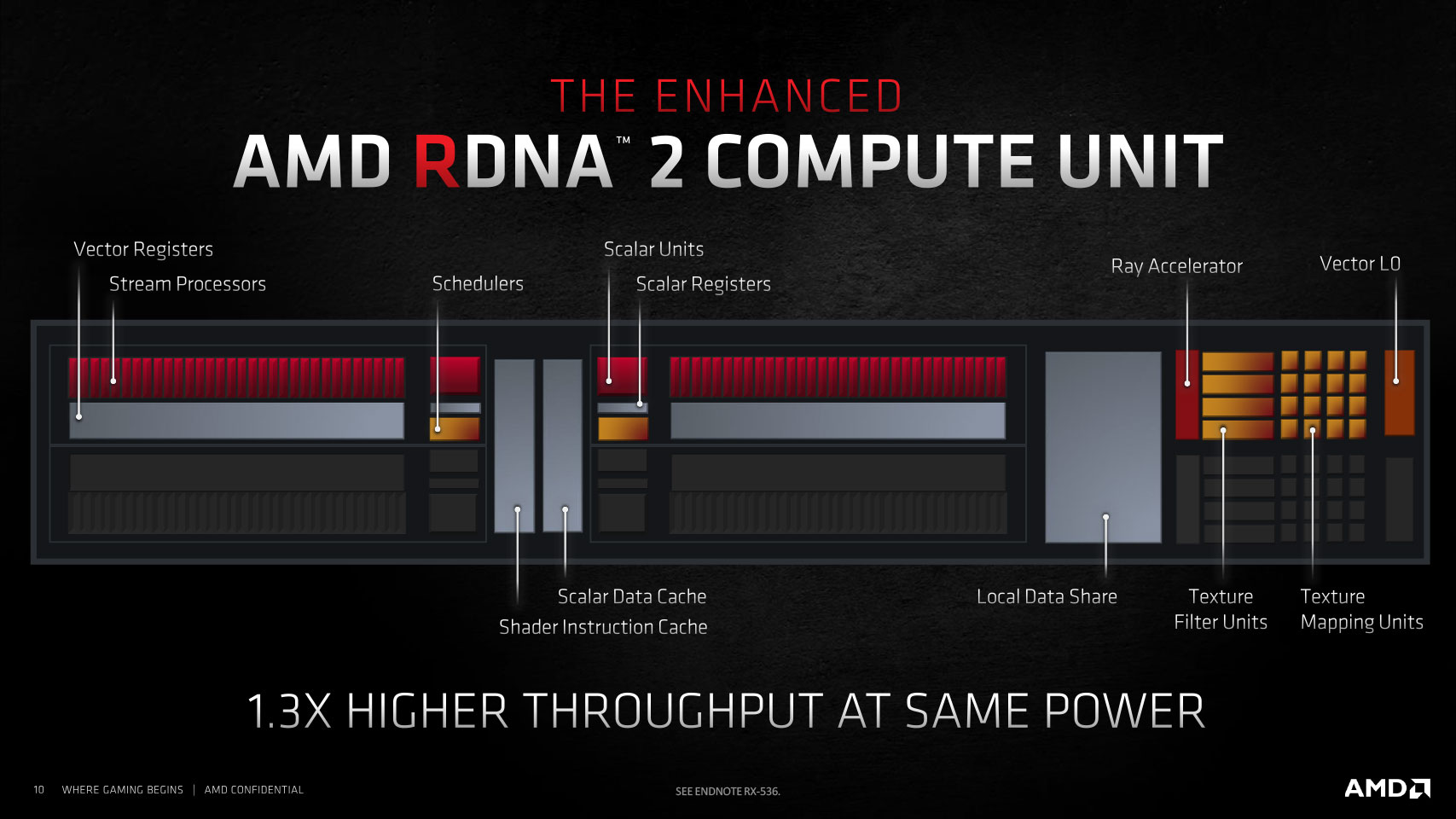

Eles podem alterar uma série de variáveis que estão aí (desde o Geometry Processor, Graphics Command Processor, ACE, etc) que irão influenciar o resto, um CU na RDNA 2 é assim

e aqui também podem alterar as coisas.

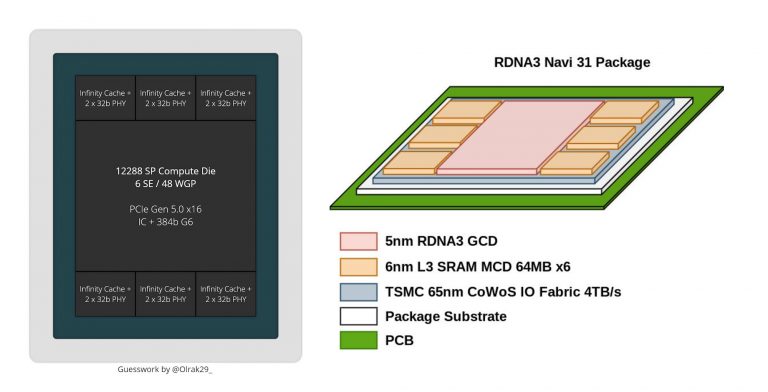

Mas do que se especula, haverá um aumento de largura do BUS e também um aumento da Infinity Cache, e isso tudo terá de ter sido "pesado e pensado" para equilibrar o resultado final e tentar espremer ao máximo.

.jpg)