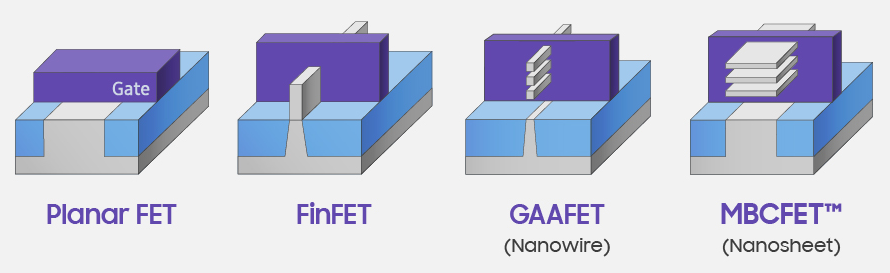

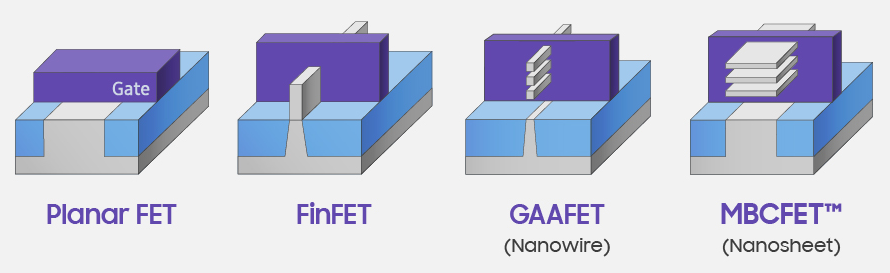

Com uma variante de transístores gate-all-arround a que chamam de Multi-Bridge Channel:

Noticia na Anandtech

Preparem-se para 100 núcleos a 10GHz nos telemóveis! J/K

J/K

Noticia na Anandtech

Preparem-se para 100 núcleos a 10GHz nos telemóveis!

J/K

J/K