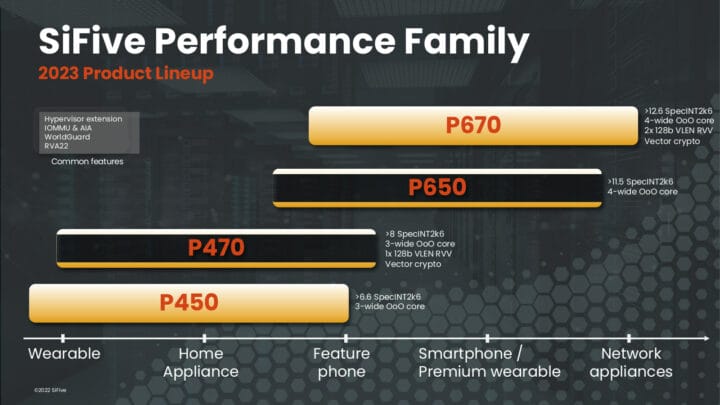

SiFive P670 and P470 RISC-V processors feature RISC-V Vector Extensions

The SiFive Performance P470 and P670 share the following features:

- Full RISC-V RVA22 profile compliance

- Full, Out-of-Order, RISC-V Vector implementation, based on the ratified RISC-V Vector v1.0 Specification

- RISC-V Vector Cryptography extensions

- SiFive WorldGuard system security

- Support for virtualization, including a separate IOMMU for accelerating virtualized device IO

- Advanced Interrupt Architecture (AIA) compliant interrupt controller with better support for Message Signal Interrupts (MSI) and virtualization

- Enhanced scalability with fully coherent multi-core, multi-cluster, with support for up to 16 cores

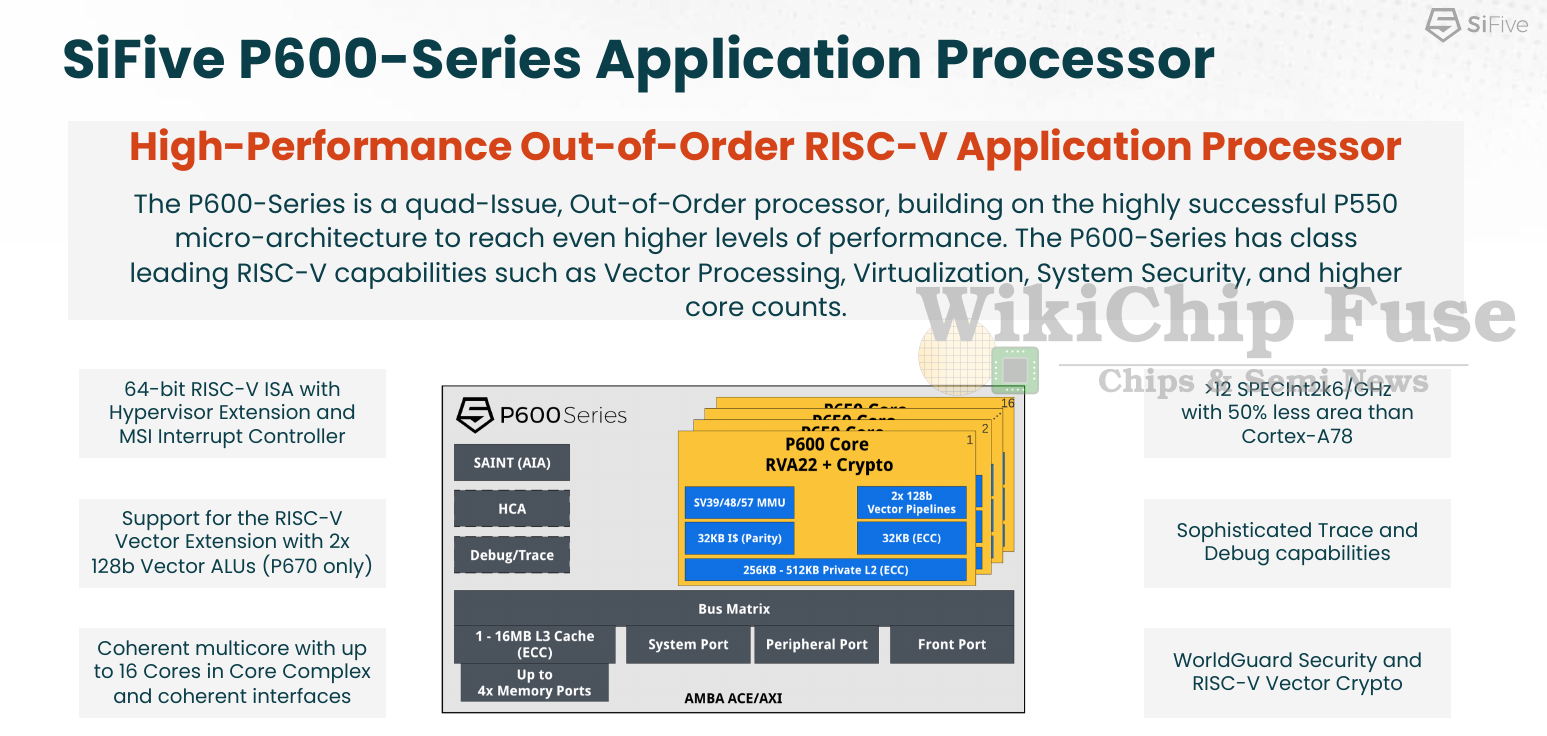

SiFive Performance P670

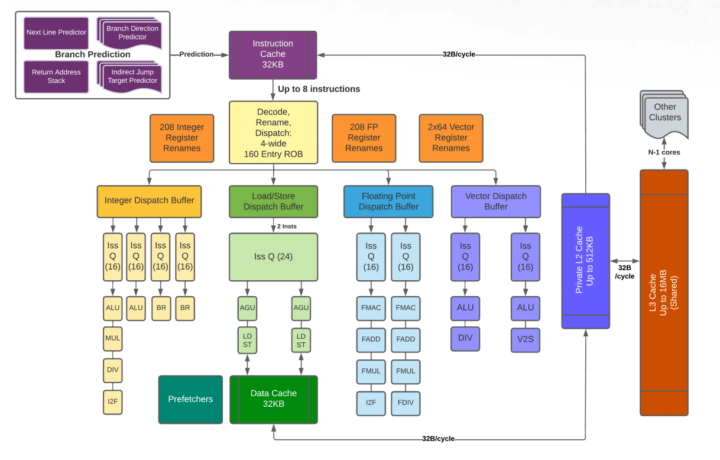

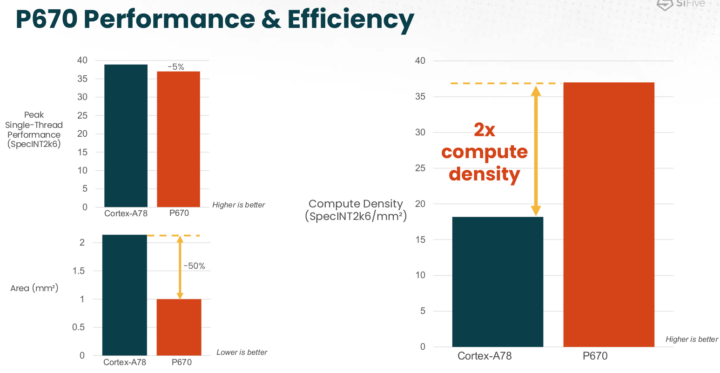

The SiFive Performance P670 core is comparable to the Arm Cortex-A78, can achieve a frequency of up to 3.4 GHz when manufactured with a 5nm process, delivers a performance of more than 12 SpecINT2k6/GHz, as well as higher single thread performance and twice the compute density compared to “legacy solution” (aka Cortex-A78), and embeds two 128-bit Vector ALUs compliant with the ratified RISC-V Vector v1.0 specification. It will be found in premium wearables, networking, robotics, and mobile SoCs, and is an upgrade to the SiFive Performance P650, which lacks the Vector Extensions.

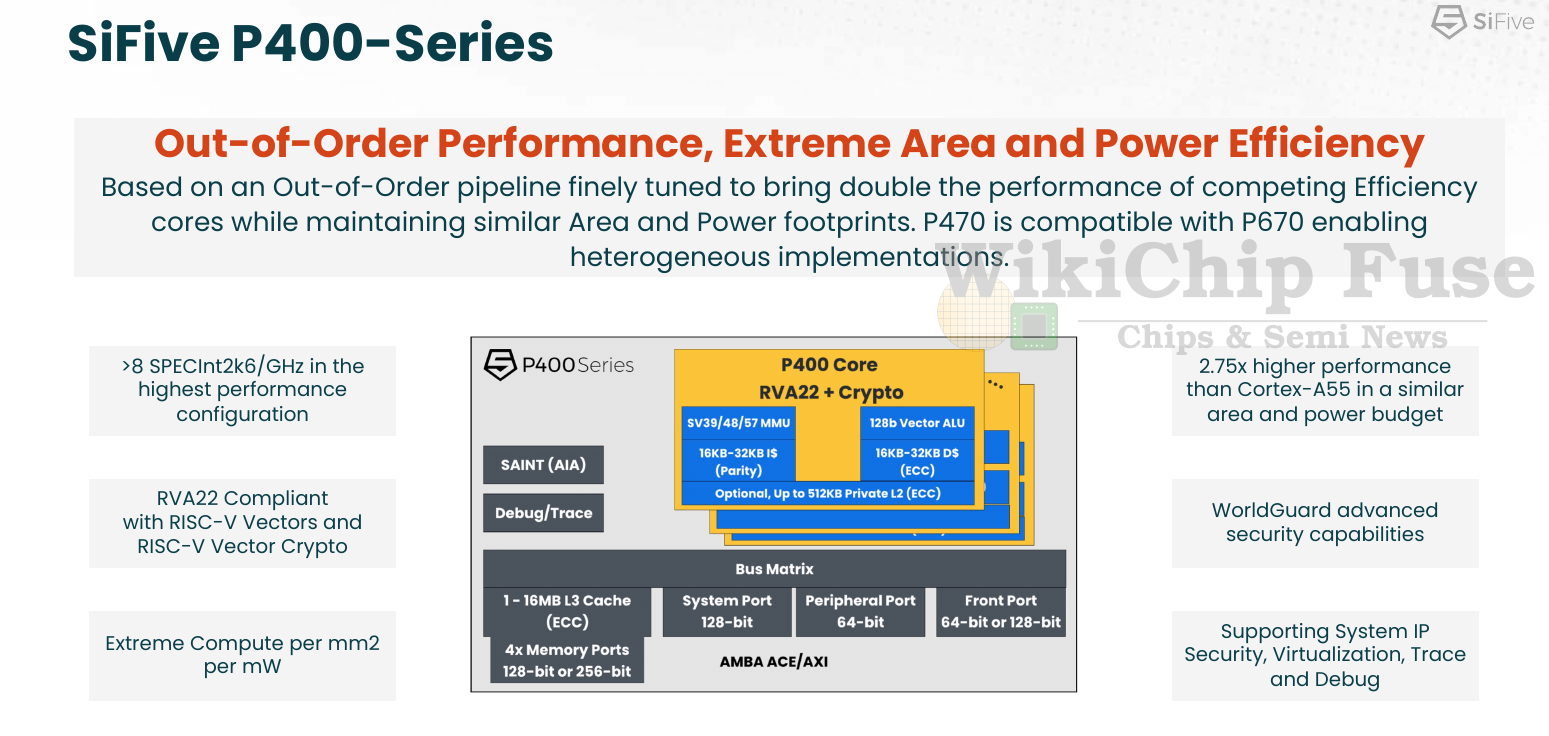

SiFive Performance P470

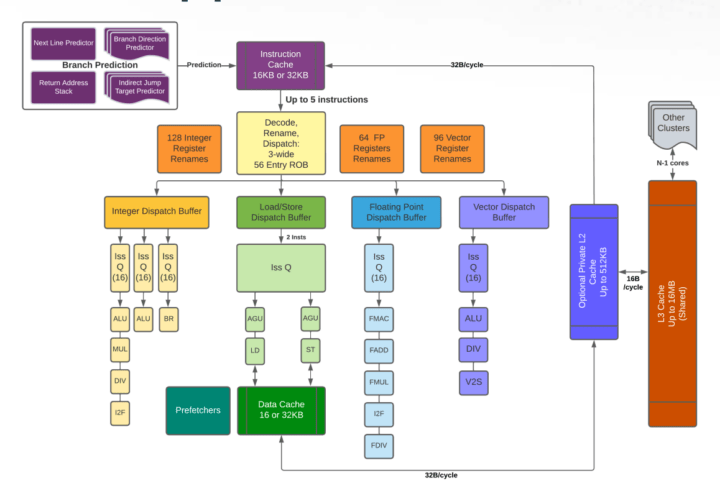

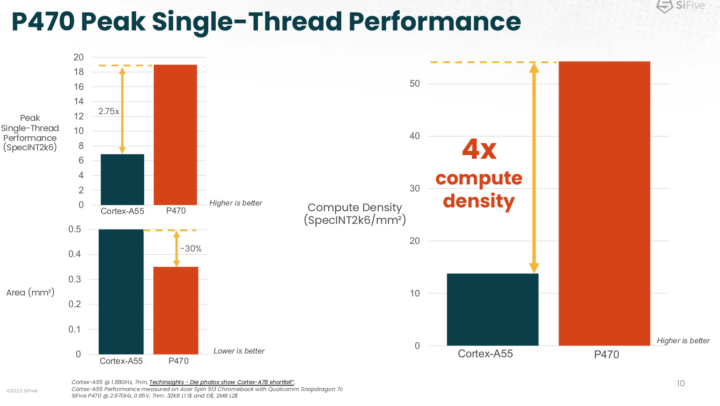

The SiFive Performance P470 core will compete against the Arm Cortex-A55 core, yet it is said to also achieve up to 3.4GHz with a 5nm process. It also offers 8+ SpecINT2k6/GHz within a small area and power envelope, as well as four times the compute density of”a leading competitor” also known as Cortex-A55… While the P670 includes two 128-bit RISC-V Vector ALU, the P470 embeds only one. SiFive will also release the P450 with the similar specifications as the P470 minus the Vector Unit.

https://www.cnx-software.com/2022/1...sc-v-processors-add-risc-v-vector-extensions/

SiFive Announces New Cores, BiFurcates Line Into Performance And Efficiency Cores

A new significant feature that comes with the P670 is support for the RISC-V Vector 1.0 specification. The P670 integrates two 128-bit vector units. It’s worth noting that SiFive also offers a trimmed-down version of the P670 called the P650 which simply excludes the vector units for customers that do not require the additional vector capabilities or for customers that are more area constrained.

The P470 achieves this by inheriting much of the P550 design but optimizing for power efficiency and area. The result is a high-performance core – comparable in performance to the P550 – but at nearly one-fourth the area of the P670.

Like the P670, the P470 comes with support for the RISC-V Vector 1.0 specification. It comes with a single 128-bit vector unit. There is also a vector-less version, the P450 – which excludes the vector unit for extremely area-constrained customers.

https://fuse.wikichip.org/news/7318...s-line-into-performance-and-efficiency-cores/

)

)