Nemesis11

Power Member

Novas instruções. Intel APX e AVX10.

APX:

https://www.phoronix.com/news/Intel-APX

https://www.phoronix.com/news/Intel-AVX10

https://www.intel.com/content/www/u...ical/advanced-performance-extensions-apx.html

APX:

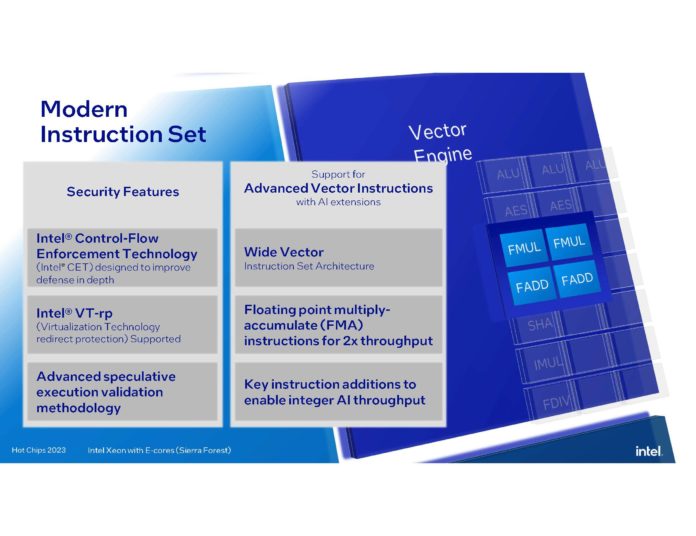

AVX10:Intel APX ultimately comes down to 16 more general purpose registers, three-operand instruction formats with a new data destination register for many integer operations, conditional ISA improvements, optimized register state save/restore operations, and a new 64-bit absolute direct jump instruction.

Overall this Intel Advanced Performance Extensions sounds very promising from the performance perspective and great that the compiler enablement is a low barrier and that from the user-space software application side should just be a matter of recompiling software without any expected code changes.

Intel Advanced Vector Extensions 10 (AVX10) is a new ISA that includes "all the richness" of AVX-512 and additional features/capabilities while being able to work for both P and E cores. Intel says AVX10 will be "the vector ISA of choice" moving into the future.

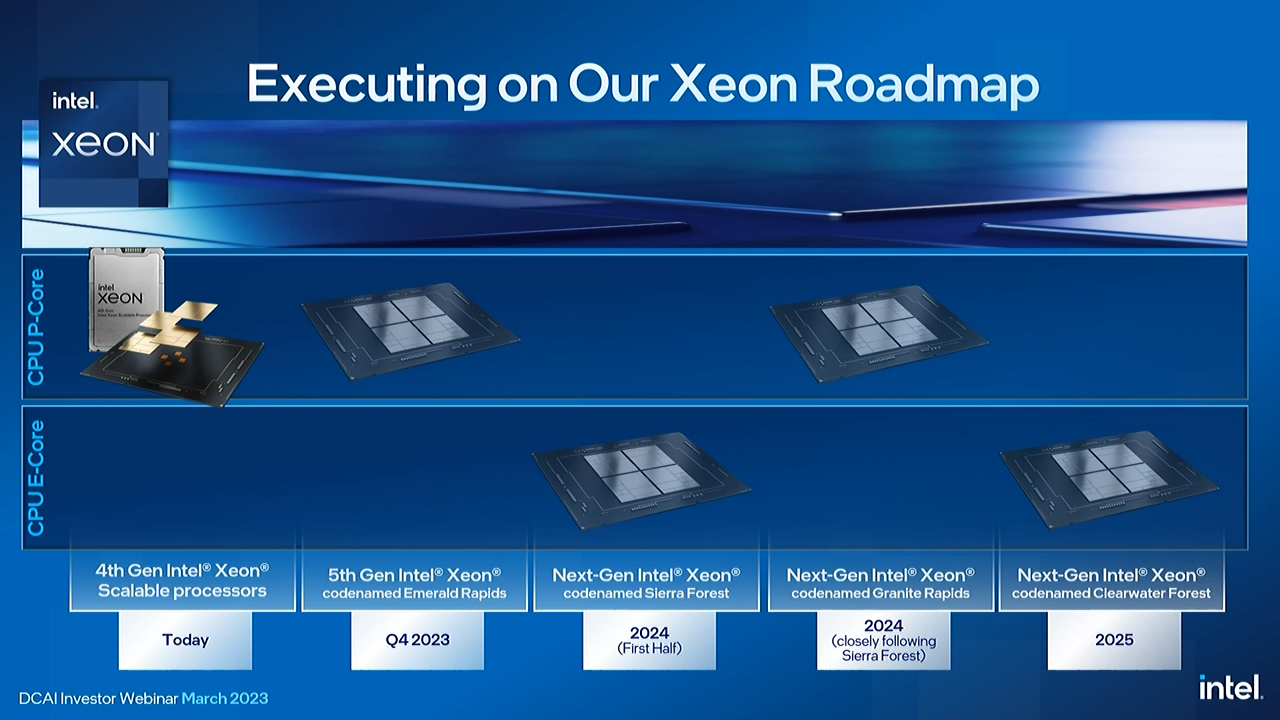

AVX10 is a super-set of AVX-512 and will be supported on all future Intel processors. Intel noted that next year's Granite Rapids server processors will feature forward-compatible support for AVX10.

Part of making AVX10 suitable for both P and E cores is that the converged version has a maximum vector length of 256-bits and found with the E cores while P cores will have optional 512-bit vector use.

https://www.phoronix.com/news/Intel-APX

https://www.phoronix.com/news/Intel-AVX10

https://www.intel.com/content/www/u...ical/advanced-performance-extensions-apx.html

final de 2023 e....

final de 2023 e....