Nemesis11

Power Member

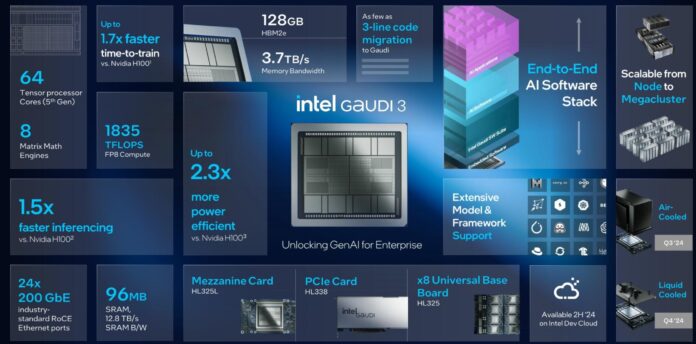

Quase 15 MB de SRAM (tirando a L1+L2) por Core?

Parece que, em próximas gerações, a Intel irá separar a L3 do Core, além do IO, para permitir flexibilidade e usar diferentes processos de fabrico.

On the packaging side, for Clearwater Forest, Intel says that it is going to use other process nodes for SRAM and I/O that do not scale as well on newer processes. AMD has its IO Die introduced with the EPYC 7002 series “Rome” on a different process for I/O. AMD also has 3D V-Cache we first reviewed with Milan-X and then Genoa-X. Our guess is that AMD is going to have to introduce a similar cache technology for future cloud-native CPU versions because everyone in the industry is running into the reality that SRAM is not scaling. Intel’s version, however, appears to put dies with cores atop cache dies.

Este Clearwater Forest, terá algumas novidades. A nível de packaging:

Intel is planning to use Foveros Direct 3D which involves direct die-to-die copper bonding between top tiles and base dies. When we look at the pictures of Clearwater Forest above, we can see the compute dies on what are likely SRAM and fabric base dies.

Another packaging technology coming on Clearwater Forest is Intel EMIB 3.5D. Here, Intel is combining several of its technologies like its EMIB (chip-to-chip bridge) and Foveros Direct 3D is called EMIB 3.5D.

A nível do processo de fabrico:

RibbonFET has the transistor gate wrapped around the channel, and these can also be made in different widths. The result is a more efficient transistor.

The second big technology is the PowerVIA. Intel is delivering backside power which we heard multiple folks at the Foundry event this week say they expect about 6% improvements just from that alone.

Render do Clearwater Forest:

https://www.servethehome.com/intel-clearwater-forest-is-set-to-be-a-tech-breakthrough-server-chip/Clearwater Forest is currently set to be the leading Intel 18A Xeon processor incorporating that node’s set of technologies as well as advanced packaging. Another way of saying it, we expect more cores with more performance and better power efficiency.

Este 18A penso que deverá ser equivalente aos 2 nm TSMC.